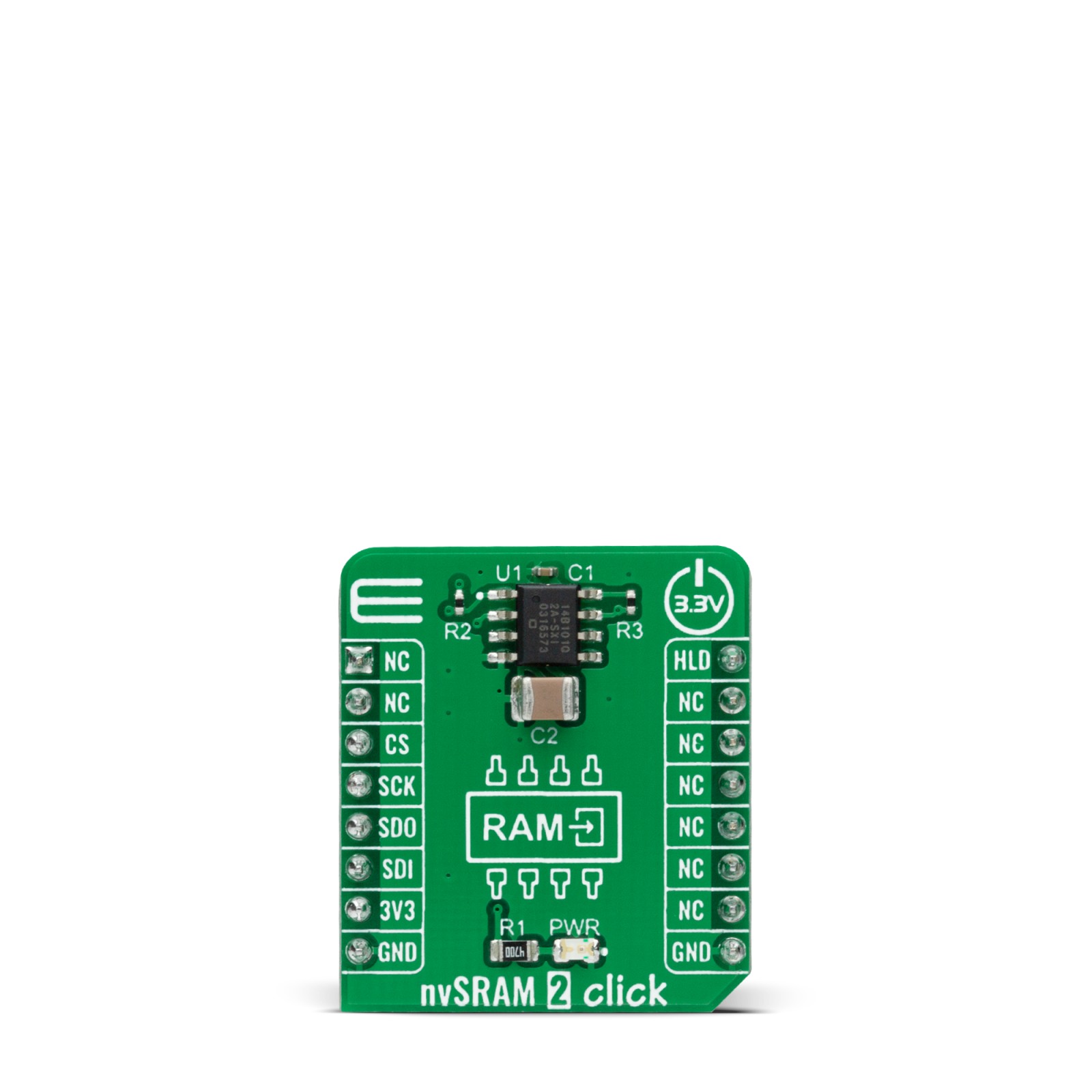

nvSRAM 2 Click

R650.00 ex. VAT

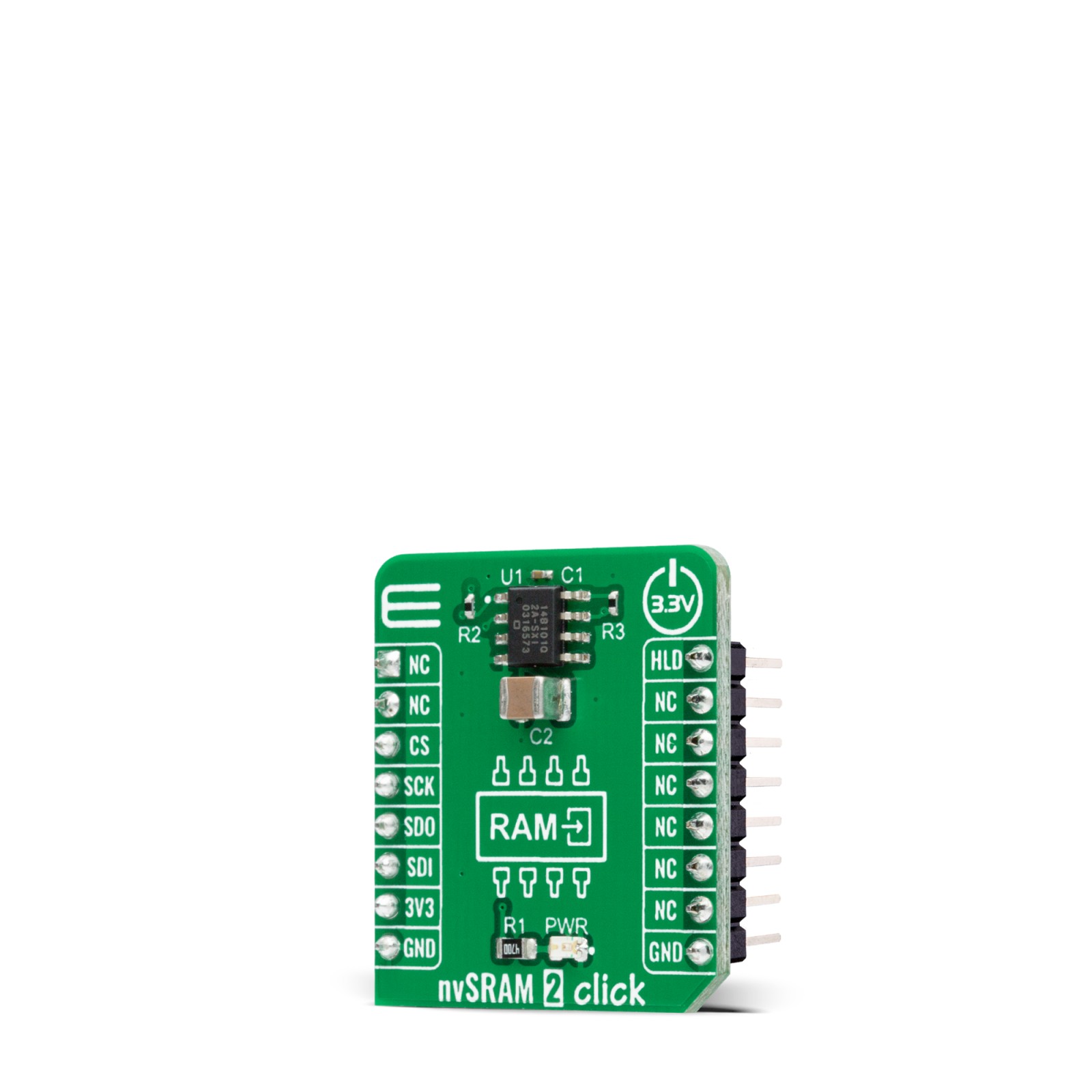

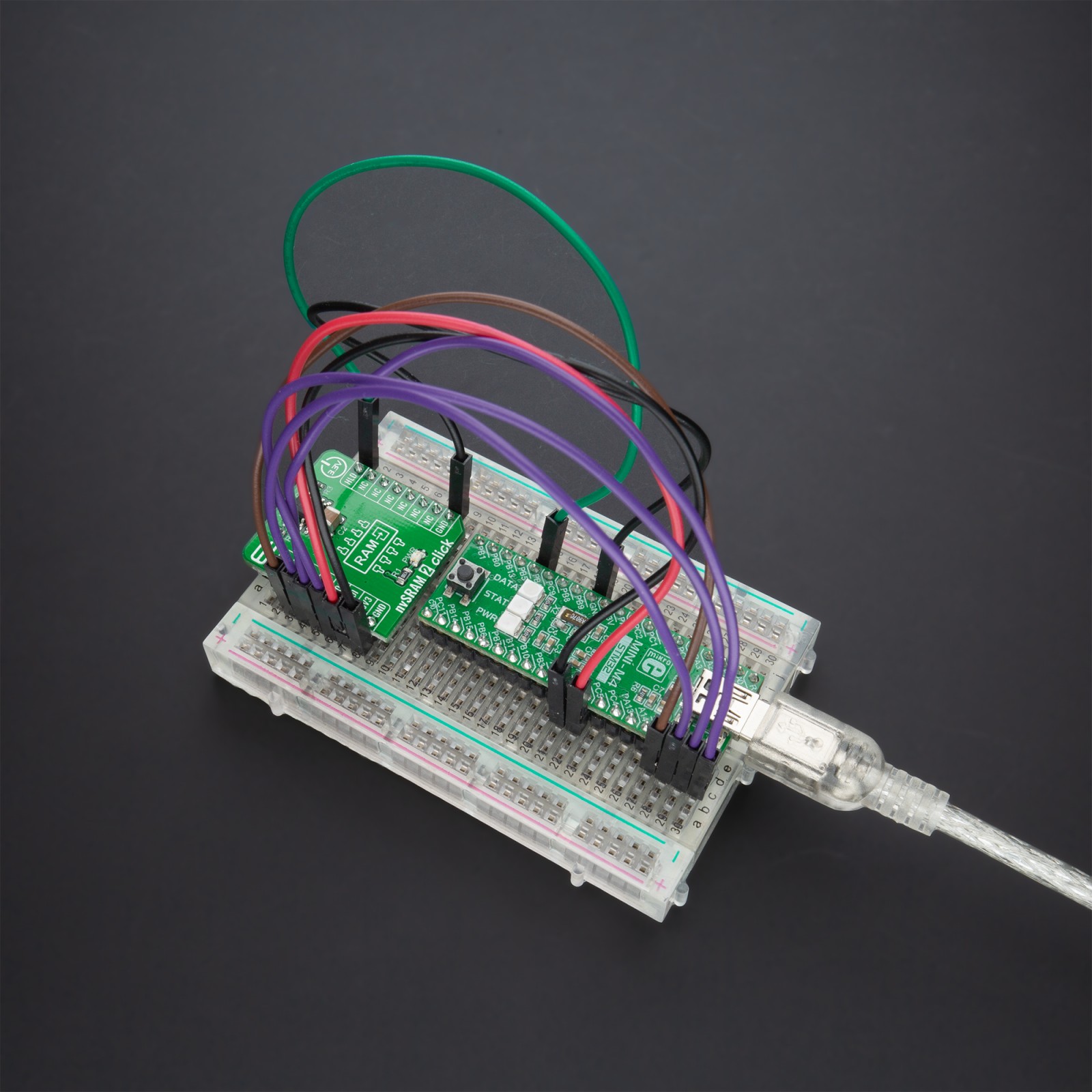

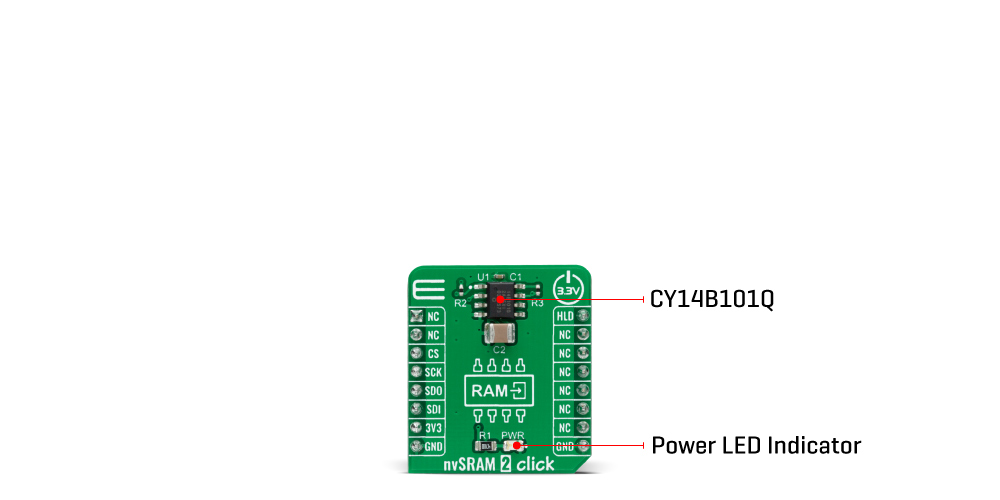

nvSRAM 2 Click is a compact add-on board that contains the most reliable nonvolatile memory. This board features the CY14B101Q, a 1Mbit nvSRAM organized as 128K words of 8 bits each with a nonvolatile element in each memory cell from Infineon. The embedded nonvolatile elements incorporate the QuantumTrap technology and provide highly reliable nonvolatile storage of data. Data transfer, initiated by the user through SPI commands, from SRAM to the nonvolatile elements takes place automatically at Power-Down. On the other hand, during the Power-Up, data is restored to the SRAM from the nonvolatile memory. This Click board™ is suitable for all applications that require fast access and high reliability of stored data, and unlimited endurance.

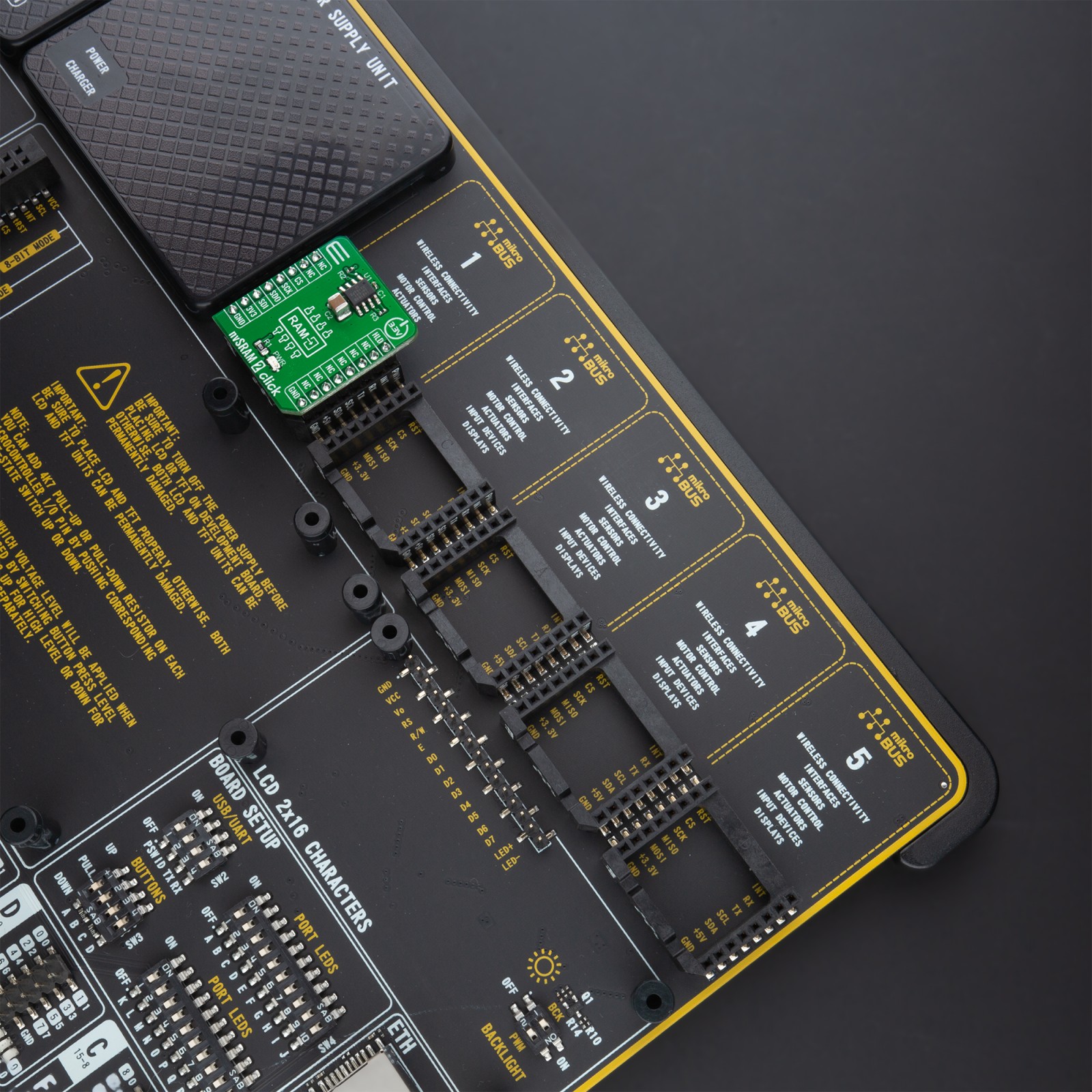

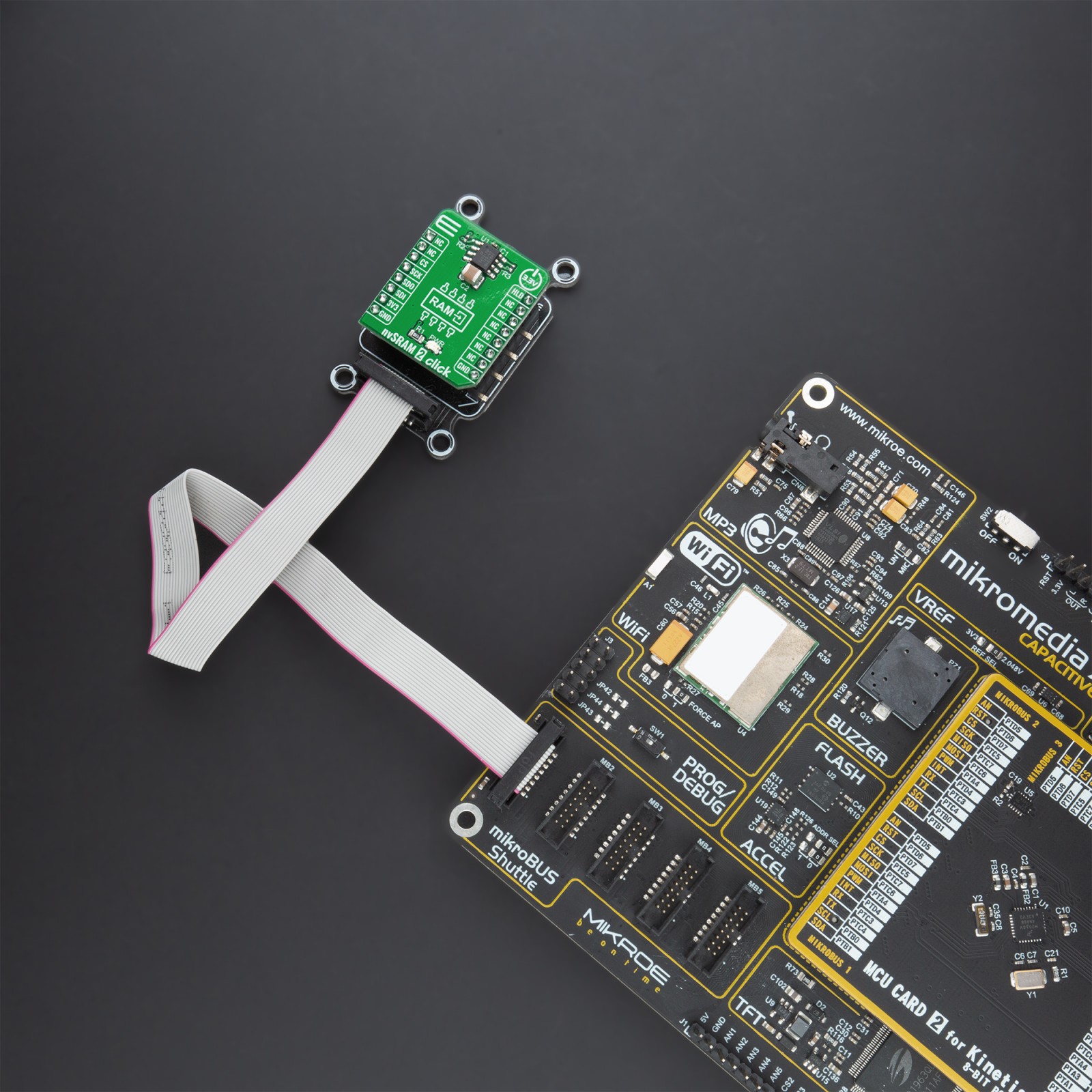

nvSRAM 2 Click is supported by a mikroSDK compliant library, which includes functions that simplify software development. This Click board™ comes as a fully tested product, ready to be used on a system equipped with the mikroBUS™ socket.

Stock: Lead-time applicable.

| 5+ | R617.50 |

| 10+ | R585.00 |

| 15+ | R552.50 |

| 20+ | R531.70 |