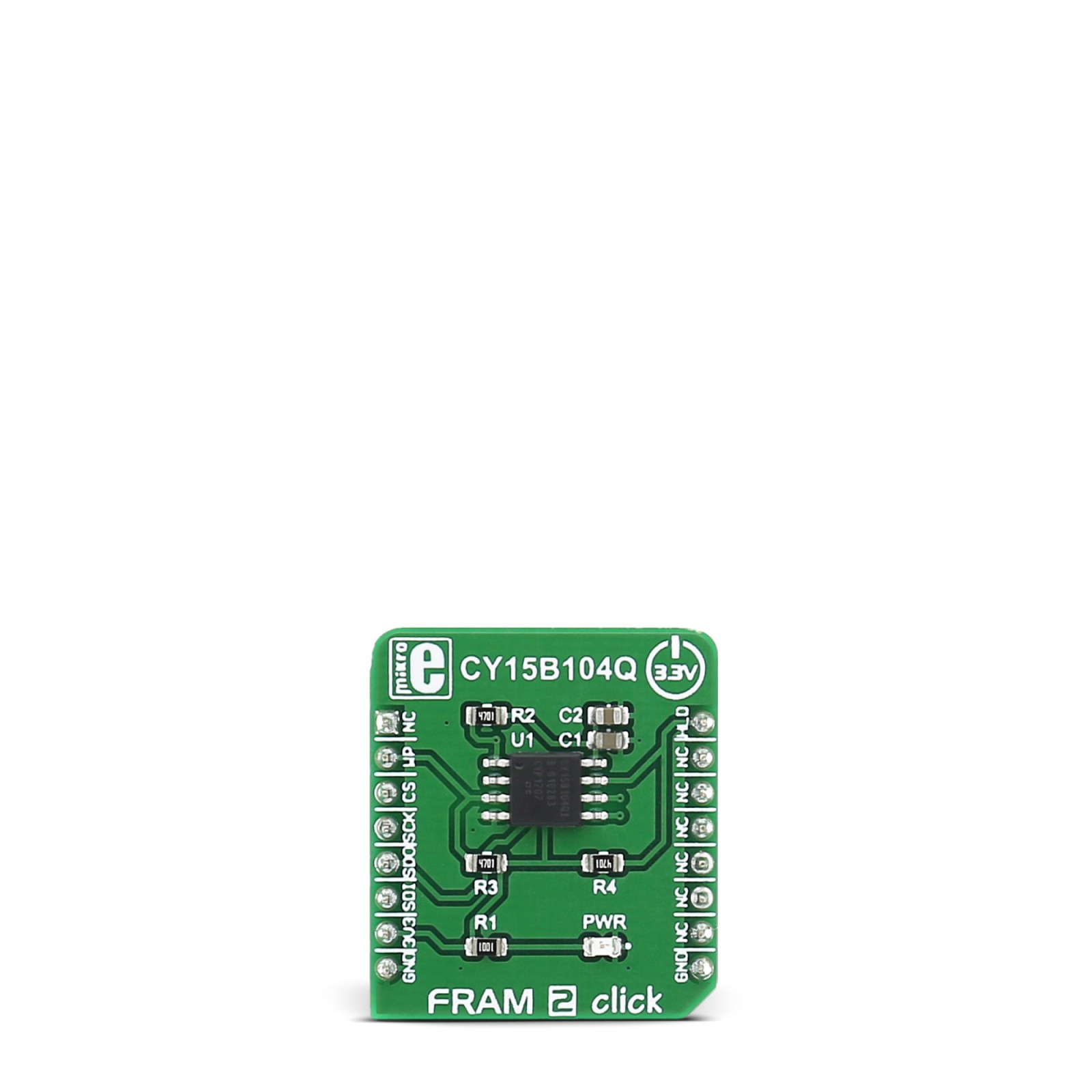

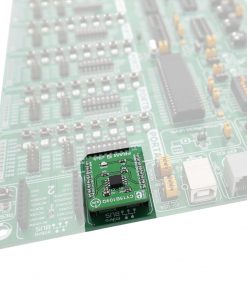

FRAM 2 Click

R1,150.00 ex. VAT

FRAM 2 click carries a ferroelectric RAM module. Ferroelectric RAM, also known as FRAM, is a non-volatile memory type, with characteristics comparable to much faster DRAM memory modules. It offers much faster alternative to common serial FLASH and EEPROM modules, which use the conventional technologies. FRAM 2 click uses the CY15B104Q, a 4 Mbit serial FRAM module from Cypress. Although the FRAM is still being developed, this company managed to provide a very reliable and fast FRAM module that can write data at bus speed, has an extremely high endurance of 1014 read/write cycles, data retention period of 151 years, and very fast SPI interface.

Stock: Lead-time applicable.

| 5+ | R1,092.50 |

| 10+ | R1,035.00 |

| 15+ | R977.50 |

| 20+ | R940.70 |

FRAM 2 click carries a ferroelectric RAM module. Ferroelectric RAM, also known as FRAM, is a non-volatile memory type, with characteristics comparable to much faster DRAM memory modules. It offers much faster alternative to common serial FLASH and EEPROM modules, which use the conventional technologies. FRAM 2 click uses the CY15B104Q, a 4 Mbit serial FRAM module from Cypress. Although the FRAM is still being developed, this company managed to provide a very reliable and fast FRAM module that can write data at bus speed, has an extremely high endurance of 1014 read/write cycles, data retention period of 151 years, and very fast SPI interface.

Besides the unique technology used for the data storage, this device kept the backward compatibility, in sense of communication and operation. Offering these advanced features, as well as a range of standard features found on most EEPROM or FLASH modules, the FRAM 2 click is ideal for nonvolatile memory applications, requiring frequent or rapid writes. It can be used for a wide range of applications, from data collection, where the number of write cycles may be critical, to demanding industrial controls, where the long write time of serial FLASH or EEPROM memory modules can cause data loss.

How does it work?

FRAM 2 click is equipped with the CY15B104Q, a 4 Mbit serial ferroelectric (FRAM) module from Cypress. It contains 4,194,304 bits of memory, organized in 524,288 byes. This means that the storage area contains 512 KB of address space. This memory IC is manufactured using the ferroelectric technology, which has many advantages over the conventional technologies used for manufacturing EEPROM and FLASH memory modules. Ferroelectric technology is still being developed and perfected, but the advantages have already been demonstrated. This technology exploits the properties of ferroelectric materials to retain the electric field after they have been exposed to it, the same way the ferromagnetic materials retain their magnetic field. This phenomenon is employed to polarize the FRAM cells and store the information. One of the areas that still need to be improved is the thermal instability, especially on high temperatures. When the ferroelectric material reaches the Curie temperature, its properties are degraded. Therefore, the high temperature might damage the content of the FRAM module. This is illustrated by the data retention period: while working at 85˚C, the data retention period is reduced to 10 years. At 65˚C, the data retention period stretches to over 150 years. Still, combined with the endurance of 1014 read/write cycles at bus write speed, this type of memory still represents an ideal solution for applications that have to do a frequent writing to the non-volatile memory locations.

.jpg)

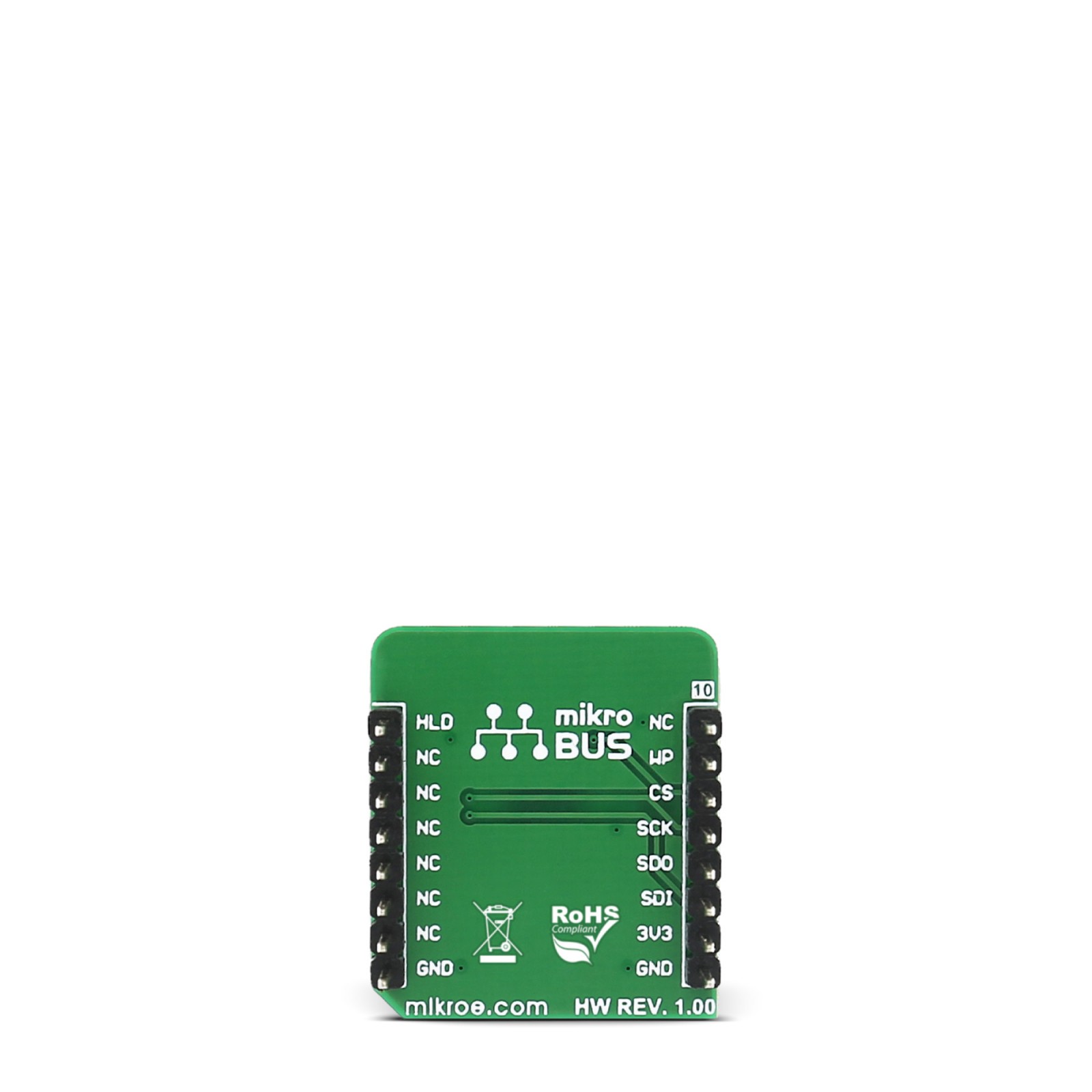

This Click board™ uses the SPI communication protocol, allowing very fast serial clock rates. To ensure reliable data transaction and to avoid accidental write to the memory array, the device employs certain protection mechanisms. Before writing any data to the IC which modifies registers or the array itself, the WEL bit must be set. This bit is cleared after or during every memory modification instruction. Therefore every memory modification instruction must be prefixed with the Write Enable (WREN) instruction that sets this bit to 1. This mechanism ensures that only the intended write instruction will be executed.

Communication with the device is initiated by the host MCU, which drives the chip select pin (#CS on the schematic) to a LOW logic level. This pin is routed to the mikroBUS™ CS pin. The next byte of information can be either command or data. Usually, the first byte is the instruction (command) followed by the memory address. Depending on the command that has been sent, either the memory is written to, or read from the specific memory address. Memory address on this device is 19 bit (0x00000 to 0x7FFFF) and therefore it is sent by 3 bytes.

There are several instruction codes, which can be sent after the CS pin being driven to a LOW logic level. These include Write Enable, Write to the memory array, Read from the memory array, Write Status Register, Read Status Register, and so on. For a full list of commands and their detailed description, please refer to the datasheet of the CY15B104Q IC.

When using the Write to array instruction, it is possible to write the whole array, while keeping the CS line to a LOW logic level, as the internal address pointer will increase with each received byte of data. Once the end of the array is reached (address 0x7FFFF) the internal pointer will rollover from the beginning (0x00000). An obvious advantage over the traditional EEPROM can be observed here: on a traditional EEPROM, the memory is organized in pages, usually 256 bytes long, which allow buffering of the data, because of the inherently slow write operation. The FRAM memory does not use pages, because the memory is written faster than the SPI bus can deliver new information (the data is written at bus speed). Therefore, no buffering is required, and the whole array can be sequentially written.

The CY15B104Q includes the write protection of the specific parts or the whole memory array. The write protection consists of two bits in the Status Register (B0, B1). The Write Status Register instruction can be used to set or reset these bits. B0 and B1 bits control the write-protect status of the memory array (from one quarter to full memory array protection). These bits are non-volatile and their state is retained between the power cycles.

The #WP pin is used to lock the Status Register. When this pin is driven to a LOW level, no further modifications to the Status register are possible and the instructions used to change bits in this register (Write Enable and Write Status Register) are completely ignored. Driving this pin to a LOW state effectively acts as the hardware memory write-protect lock mechanism. This pin can be completely disabled by the WPEN bit of the status register: if the WPEN bit is cleared (0), this pin will have no effect on the CY15B104Q IC. The #WP pin is routed to the mikroBUS™ RST pin, and it is labeled as WP.

The FRAM 2 click allows hold of the communication in progress. If the #HOLD pin is driven to a LOW logic level on the LOW pulse of the serial clock signal (SCK), the communication will be paused, but not aborted. Driving this pin to a HIGH logic level will resume the data transfer. This pin is routed to the mikroBUS™ PWM pin, labeled as HLD.

Specifications

Type

FRAM

Applications

Suitable for low-power applications

On-board modules

CY15B104Q – a 4-Mbit non-volatile memory employing an advanced ferroelectric process

Key Features

4-Mbit ferroelectric random access memory (F-RAM) logically organized as 512 K × 8, high-endurance 100 trillion (10^14) read/writes, 151-year data retention, low power consumption

Interface

GPIO,SPI

Feature

No ClickID

Compatibility

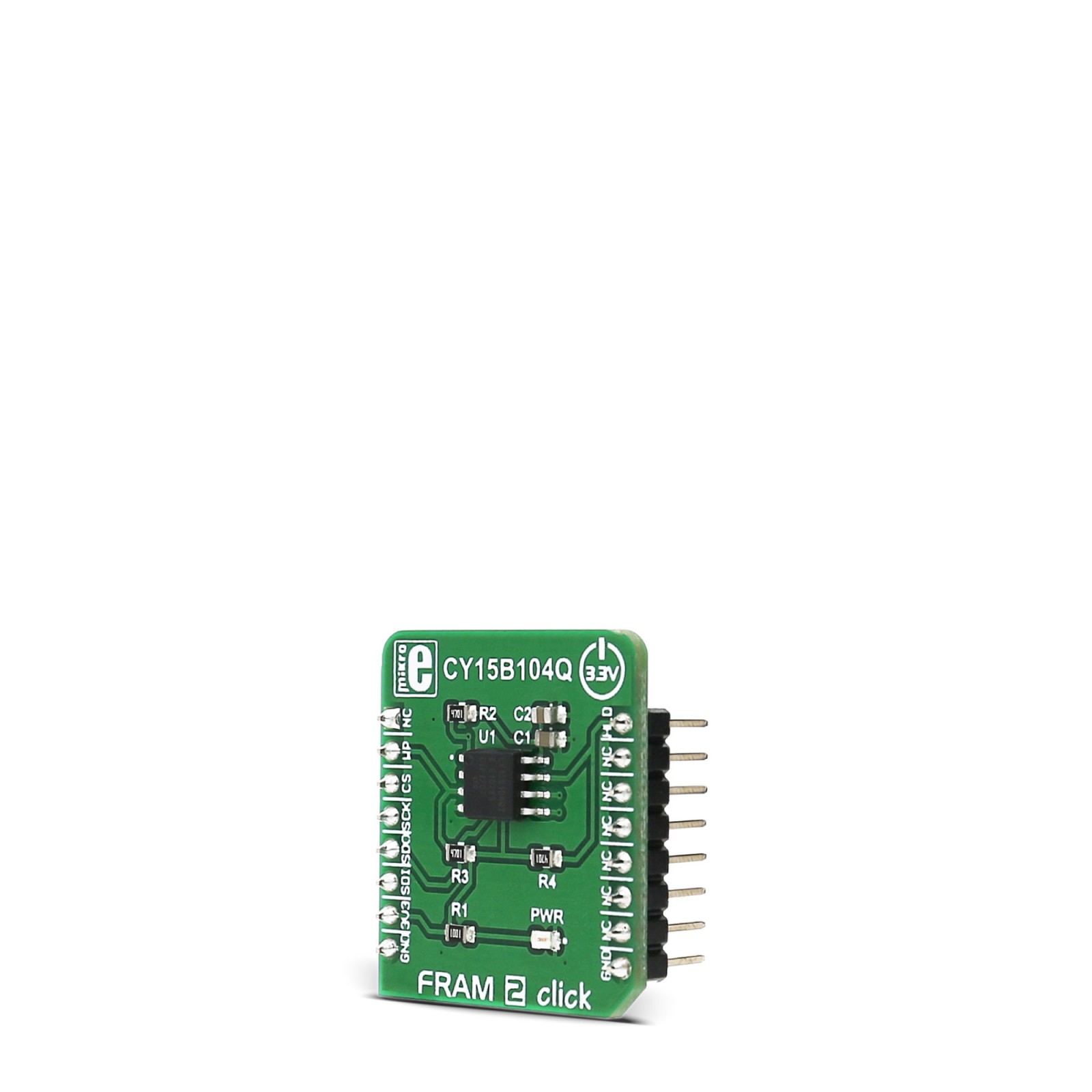

mikroBUS™

Click board size

S (28.6 x 25.4 mm)

Input Voltage

3.3V

Pinout diagram

This table shows how the pinout on FRAM 2 click corresponds to the pinout on the mikroBUS™ socket (the latter shown in the two middle columns).

Onboard settings and indicators

| Label | Name | Default | Description |

|---|---|---|---|

| LD1 | PWR | Power indication LED |

Software support

We provide a library for FRAM 2 click on our Libstock page, as well as a demo application (example), developed using MikroElektronika compilers and mikroSDK. The provided click library is mikroSDK standard compliant. The demo application can run on all the main MikroElektronika development boards.

Library Description

Key functions:

void fram_write(uint32_t address, uint8_t *buffer, uint16_t counter)- The function writes to sequential memory locations from the buffer.void fram_read(uint32_t address, uint8_t *buffer, uint16_t count)- The function reads sequential memory locations to the buffer.void fram_writeEnable()- The function enables data writing in the FRAM memory space.

Examples Description

The application is composed of three sections:

- System Initialization – GPIO and SPI module Initialization.

- Application Initialization - Fram 2 Driver Initialization, initialization of click by setting mikorBUS pins to an appropriate logic level, performing erase all and write enable functions.

- Application Task – Writing data to click memory and displaying the read data via UART.

void applicationTask()

{

mikrobus_logWrite("Writing MikroE to Fram memory, from address 0x015015:",_LOG_LINE);

fram2_write (0x015015, &wrData[0], 9);

mikrobus_logWrite("Reading 9 bytes of Fram memory, from address 0x015015:",_LOG_LINE);

fram2_read(0x015015,&rdData[0],9);

mikrobus_logWrite("Data read: ",_LOG_TEXT);

mikrobus_logWrite(rdData,_LOG_LINE);

Delay_ms(1000);

}

The full application code, and ready to use projects can be found on our Libstock page.

Other mikroE Libraries used in the example:

- UART

- SPI

Additional notes and information

Depending on the development board you are using, you may need USB UART click, USB UART 2 click or RS232 click to connect to your PC, for development systems with no UART to USB interface available on the board. The terminal available in all MikroElektronika compilers, or any other terminal application of your choice, can be used to read the message.

mikroSDK

This click board is supported by mikroSDK - MikroElektronika Software Development Kit. To ensure proper operation of mikroSDK compliant click board demo applications, mikroSDK should be downloaded from the LibStock and installed for the compiler you are using.

For more information about mikroSDK, visit the official page.

Resources

Downloads

| Weight | 25 g |

|---|---|

| Brand | MikroElektronika |