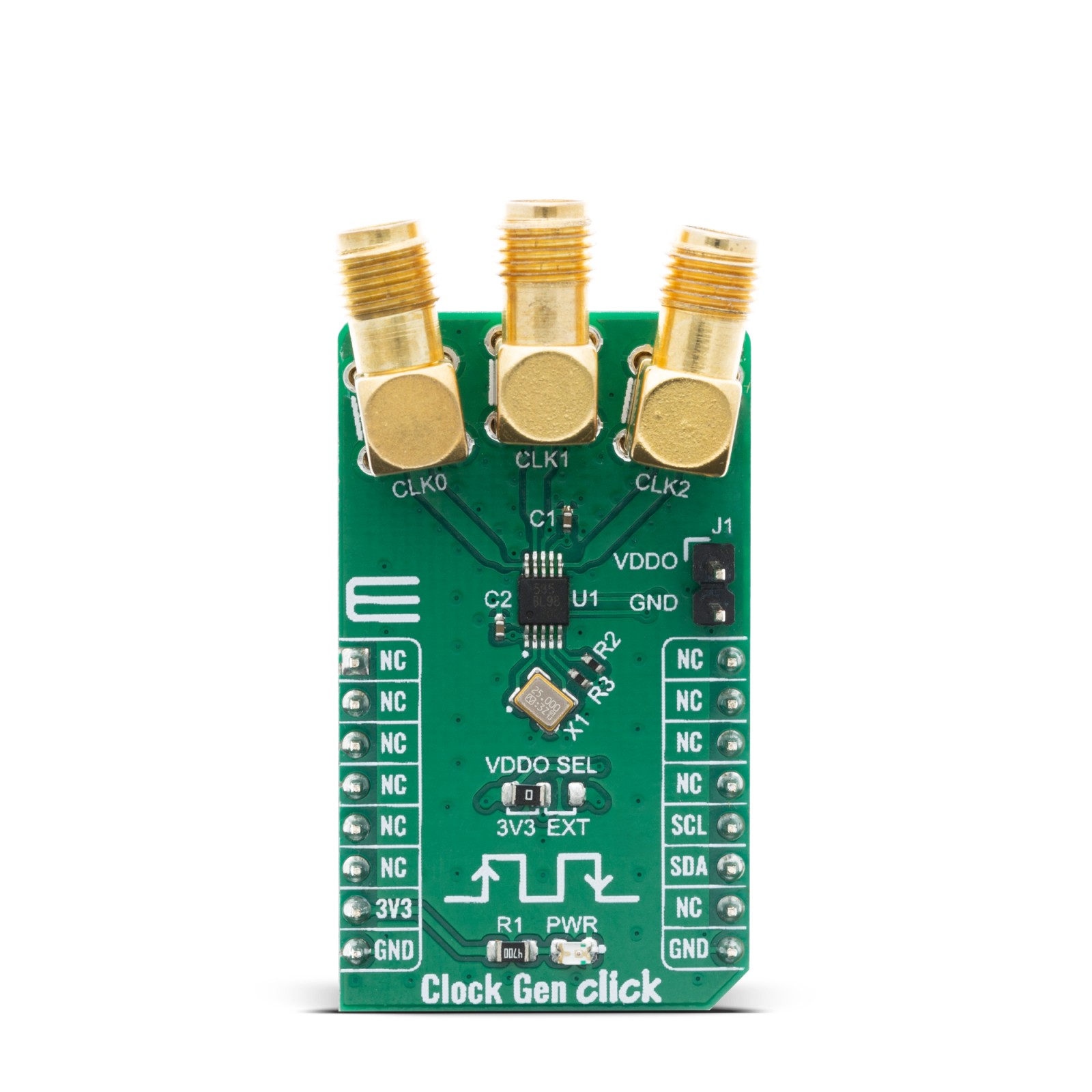

Clock Gen Click

R470.00 ex. VAT

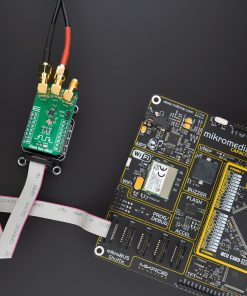

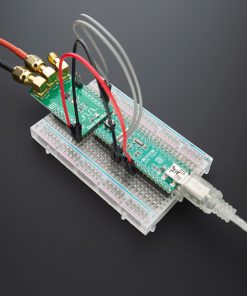

Clock Gen Click offers an ideal replacement for crystals, crystal oscillators, VCXOs, phase-locked loops (PLLs), and fanout buffers in cost-sensitive applications. This click features the Si5351A from Silicon Labs, an I2C configurable clock generator based on a PLL + high resolution MultiSynth fractional divider architecture which can generate any frequency up to 200 MHz on each of its outputs with 0 ppm error. The Si5351A is capable of generating synchronous or free-running non-integer related clock frequencies at each of its outputs (CLK0, CLK1, and CLK2), enabling one device to synthesize clocks for multiple clock domains in a design. It eliminates the need for higher cost, custom pullable crystals while providing reliable operation over a wide tuning range. The Si5351C offers the same flexibility but synchronizes to an external reference clock.

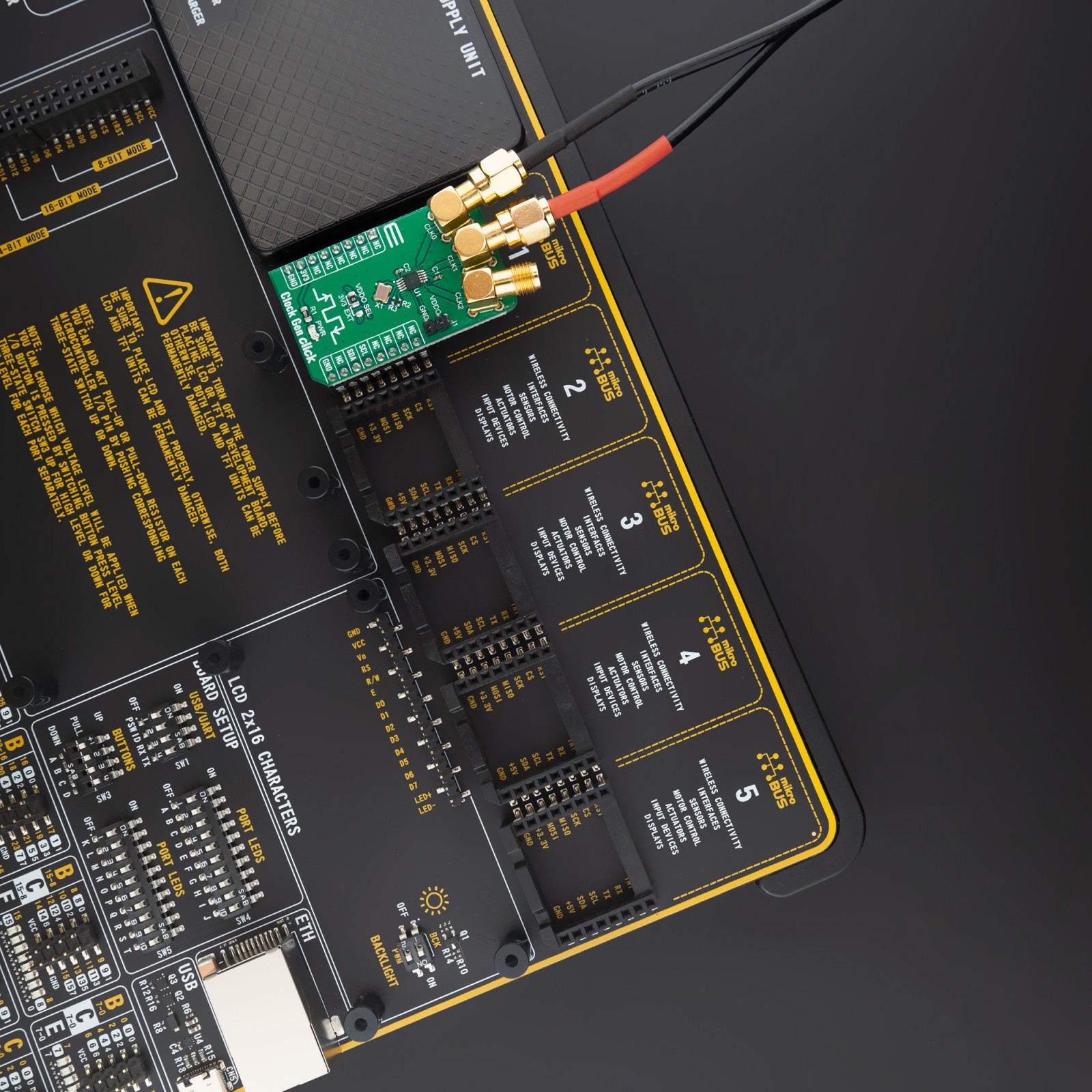

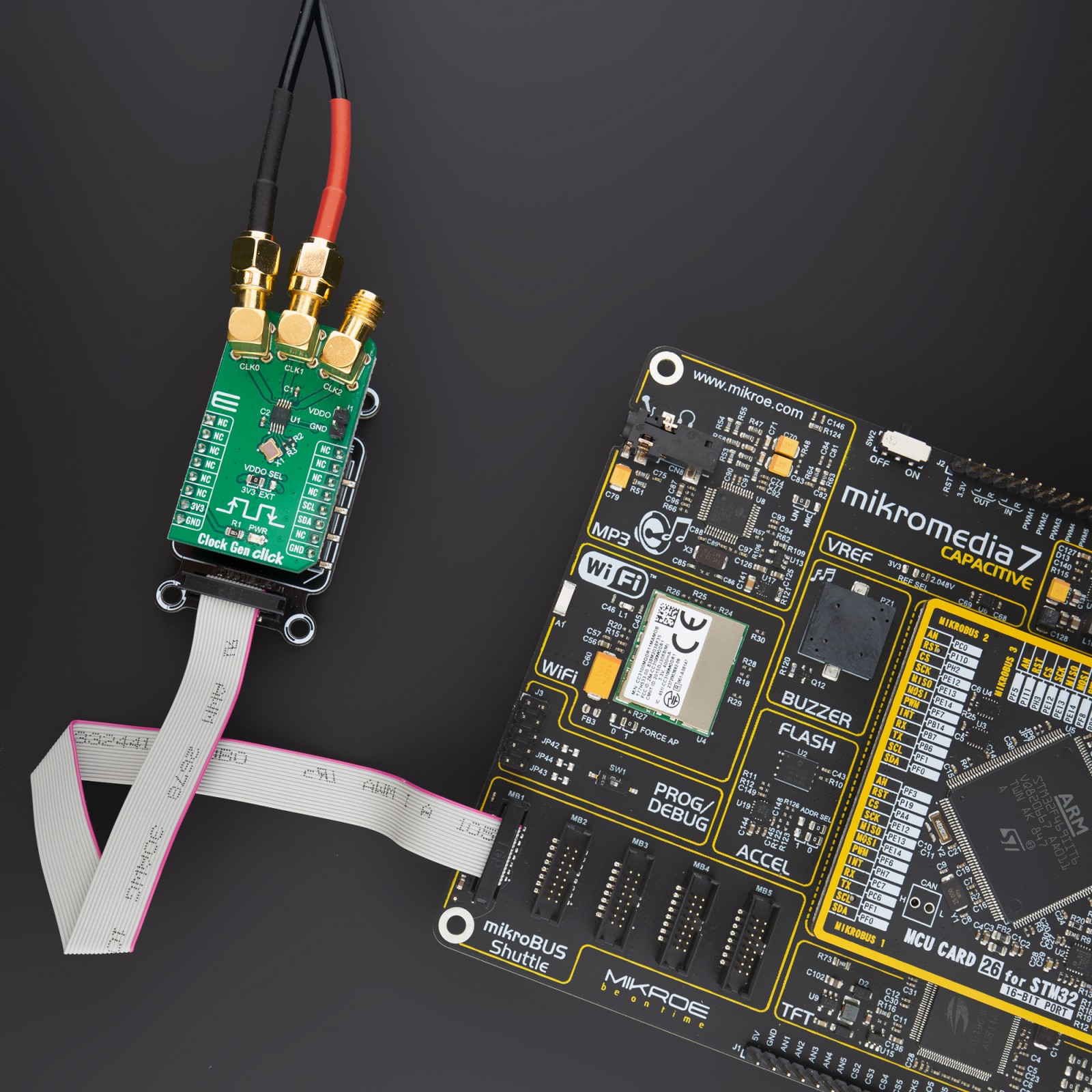

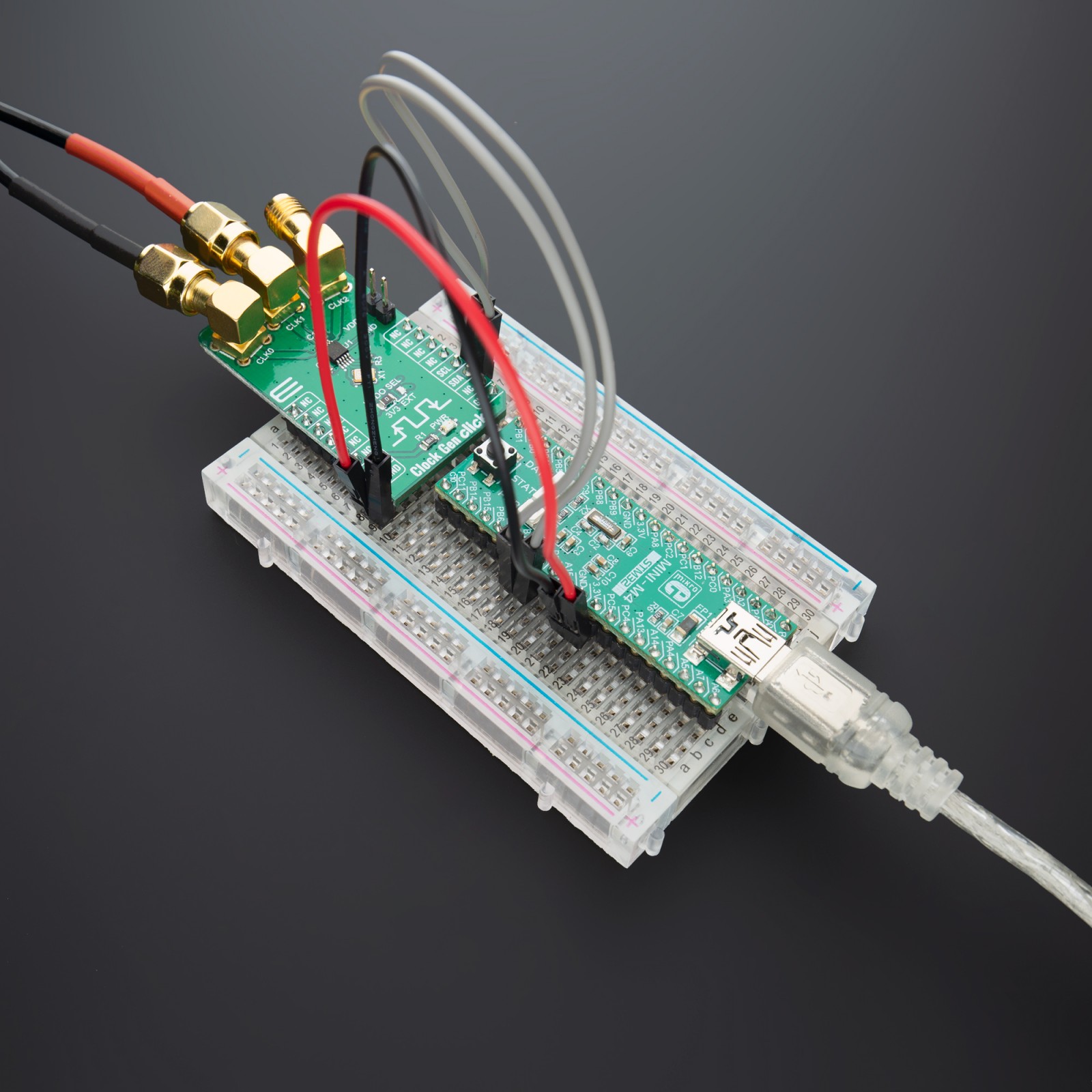

Clock Gen Click is supported by a mikroSDK compliant library, which includes functions that simplify software development. This Click board™ comes as a fully tested product, ready to be used on a system equipped with the mikroBUS™ socket.

Stock: Lead-time applicable.

| 5+ | R446.50 |

| 10+ | R423.00 |

| 15+ | R399.50 |

| 20+ | R384.46 |